Assignment No. 03View more random threads:

- CS501 Advance Computer Architecture assignment solution...

- CS507 Information Systems Assignment No. 01 SEMESTER Fall...

- CS304 Object Oriented Programming spring 2011 idea solution

- Object Oriented Programming (CS304) Assignment No.03...

- CS403 Database Management Systems Assignment No.2 Fall...

- cs304 first may spring semester for mcs 2015 final solution

- Cs401 Assignment no 5 fall January 2012 solution

- CS506 assignment no 5 fall 2010 solution 29-01-2011

- cs402 assignment no 4 fall 2010 solution

- CS401 Computer Architecture and Assembly Language...

Semester: Spring 2011

CS302: Digital Logic Design

Total Marks: 10

Due Date: 08/06/2011

Instructions:

Please read the following instructions carefully before submitting assignment:

It should be clear that your assignment will not get any credit if:

The assignment is submitted after due date.

The assignment is submitted via email.

The submitted assignment does not open or file is corrupt.

All types of plagiarism are strictly prohibited.

Objectives:

This assignment has been designed to enable you to understand the concepts of:

Flip-Flops

Flip-flops with asynchronous inputs

Counters

Guidelines:

Perform/write all steps while solving the problems.

Assignment

Question No. 1 [Marks: 7]

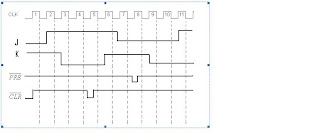

Determine Q output waveform for a negative edge triggered J-K flip-flop with preset, clear and J, K inputs. You are required to draw Q output waveform on timing diagram.

Question No. 2 [Marks: 1+2]

Provide to-the-point answers to the following questions:

a) How does a synchronous counter differ from asynchronous counter?

b) How many states does a mod-12 counter have? What is minimum number of flip-flops required?

Last edited by Vuhelper; 06-06-2011 at 08:07 PM.

what about second question

helper bhai ye to positive triggered hai assignment mein negative triggered hai

so plz solve it again

matlab harib???????

Sponsored Links

matlb ye ke assignment question mein humain negative triggered required hai positive nahi

jabk ye positive edge triggered timing diagram hai

dear plz ap khud handouts ma sy flip- flop ka lecture read kro to ap ko is ki samjh aa jay gi k kis trah krni hy assignment or negitive triggerd ka matlab hy k clock pulse zero hy or agr clock pulse zero hy to NAND gate ko ik bhi zero O/P jay gi to wo logic 1 day ga just p is ma jahan bhi Q ki o/p hight hoti hy wahan change kr do

hurry up today is the last day to submit this assignment so please

There are currently 1 users browsing this thread. (0 members and 1 guests)